PCI-SIG Completes CopprLink Cabling Standard: PCIe 5.0 & 6.0 Get Wired

by Ryan Smith on May 1, 2024 10:00 AM EST

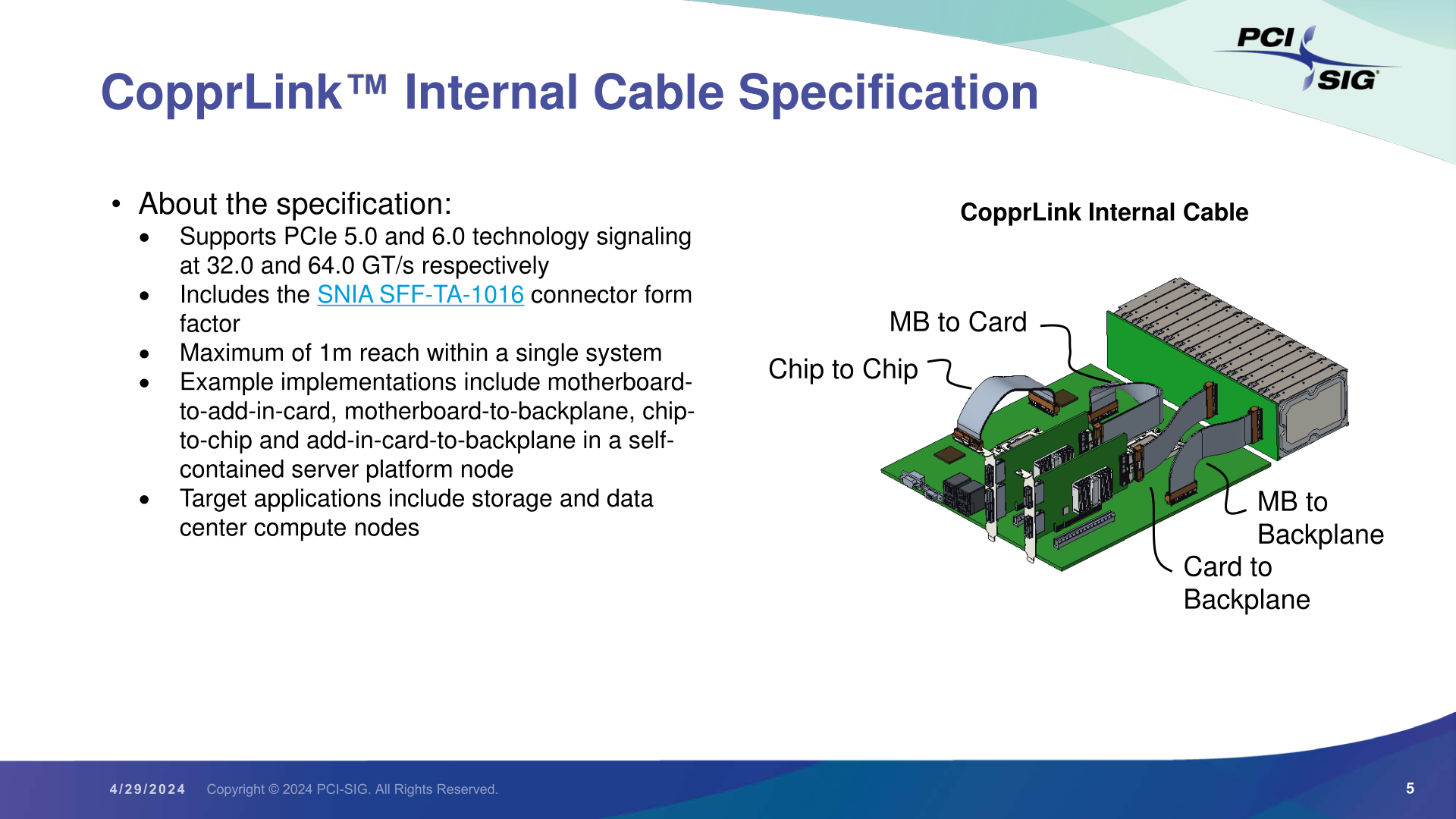

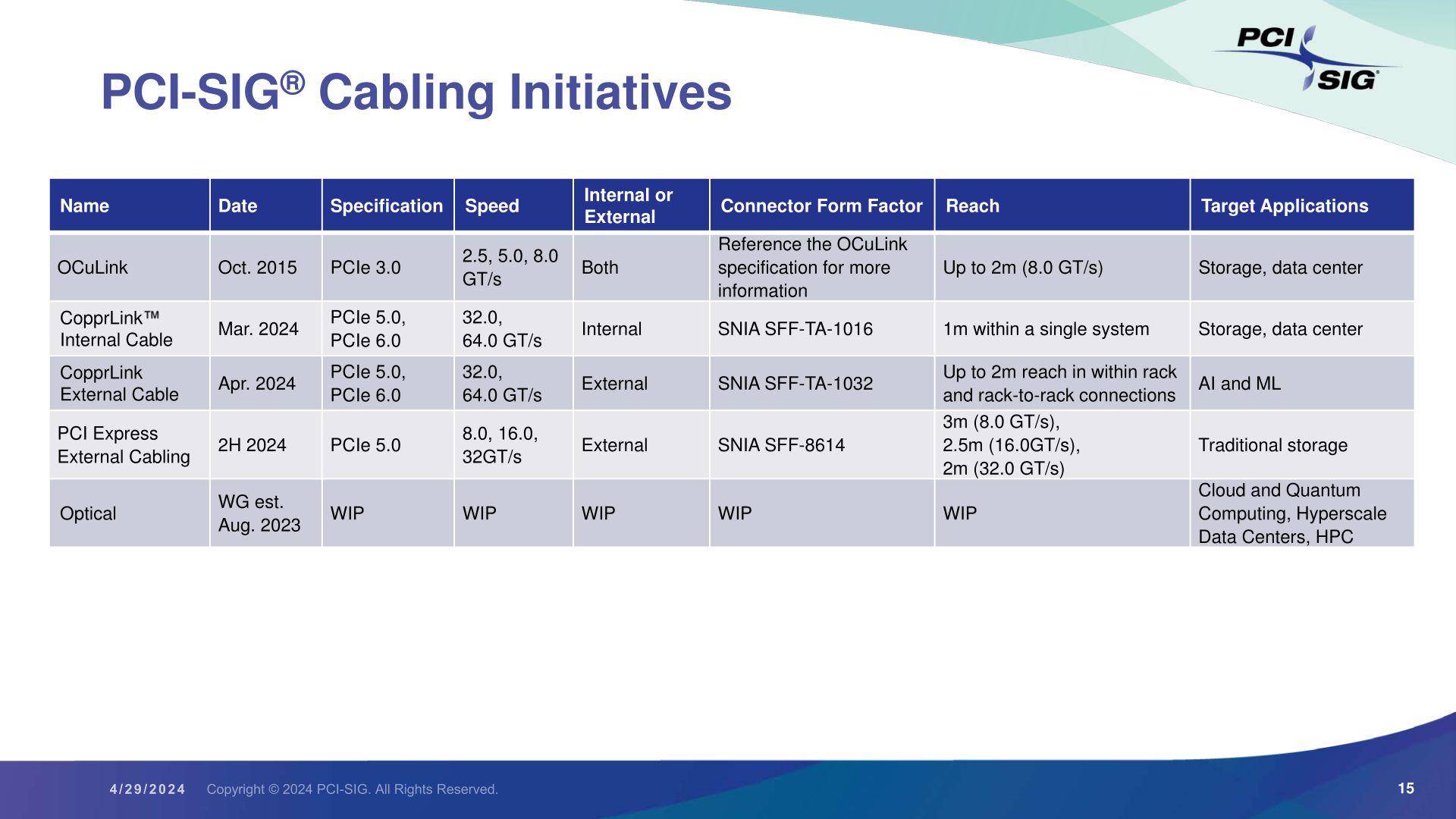

The PCI-SIG sends word over this morning that the special interest group has completed their development efforts on the group’s new PCI-Express cabling standard, CopprLink. Designed to go hand-in-hand with PCIe 5.0 and PCIe 6.0, CopprLink defines both internal and external copper cabling for the latest PCIe standards, giving system vendors and assemblers the ability to use wires to connect devices within a system, or even whole systems.

The CopprLink standard is, in practice, a pair of standards sharing the same brand-name under the PCI-SIG umbrella. The internal standard, “CopprLink Internal Cable”, is designed to allow for a new generation of PCIe cables up to 1 meter in length that are capable of sustaining PCIe 5.0 and PCIe 6.0 signaling. Internal CopprLink effectively supplants a host of older internal PCIe cabling standards (including the abandoned OCuLink), which were originally designed for earlier generations of PCIe signaling.

At a high level, internal CopprLink is intended to provide not only host-to-device connectivity, but even more transparent backhaul applications such as motherboard-to-backplane connectivity, and unique applications such as chip-to-chip PCIe connections. In other words, CopprLink allows for cabled PCIe to be used in almost any situation where a PCIe connection needs to be established within a system. Strictly speaking, CopprLink doesn't replace the PCIe CEM connector in any way – but the relatively thick copper cables have less signal loss than PCB traces, making a cabled standard extremely useful even for internal connections. PCI-SIG sees CopprLink cables taking hold in the storage and data center markets, product categories where we already see PCIe cabling in use today.

The companion connector standard for internal CopprLink is the SNIA-developed SFF-TA-1016 connector, which bears more than a passing resemblance to the widely-used SFF-8654 (SlimSAS) connector. SFF-TA-1016 is available in x4, x8, and x16 configurations, and while the PCI-SIG doesn’t go so far as to defining widths within their own standard, the connectors available paint a clear picture of the options at hand. Internal CopprLink x4 should be especially popular with storage, as we already see today.

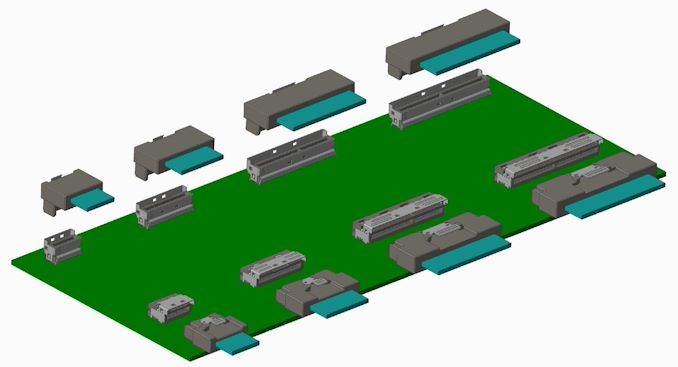

Top: SFF-TA-1016 Family of Connectors (Figure 4-1, Image Courtesy SNIA)

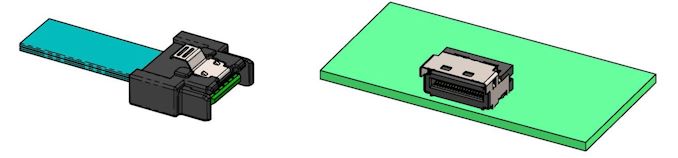

Bottom: Sample SFF-TA-1016 x4 Contact Plug and Recepticle (Figure 4-2, Image Courtesy SNIA)

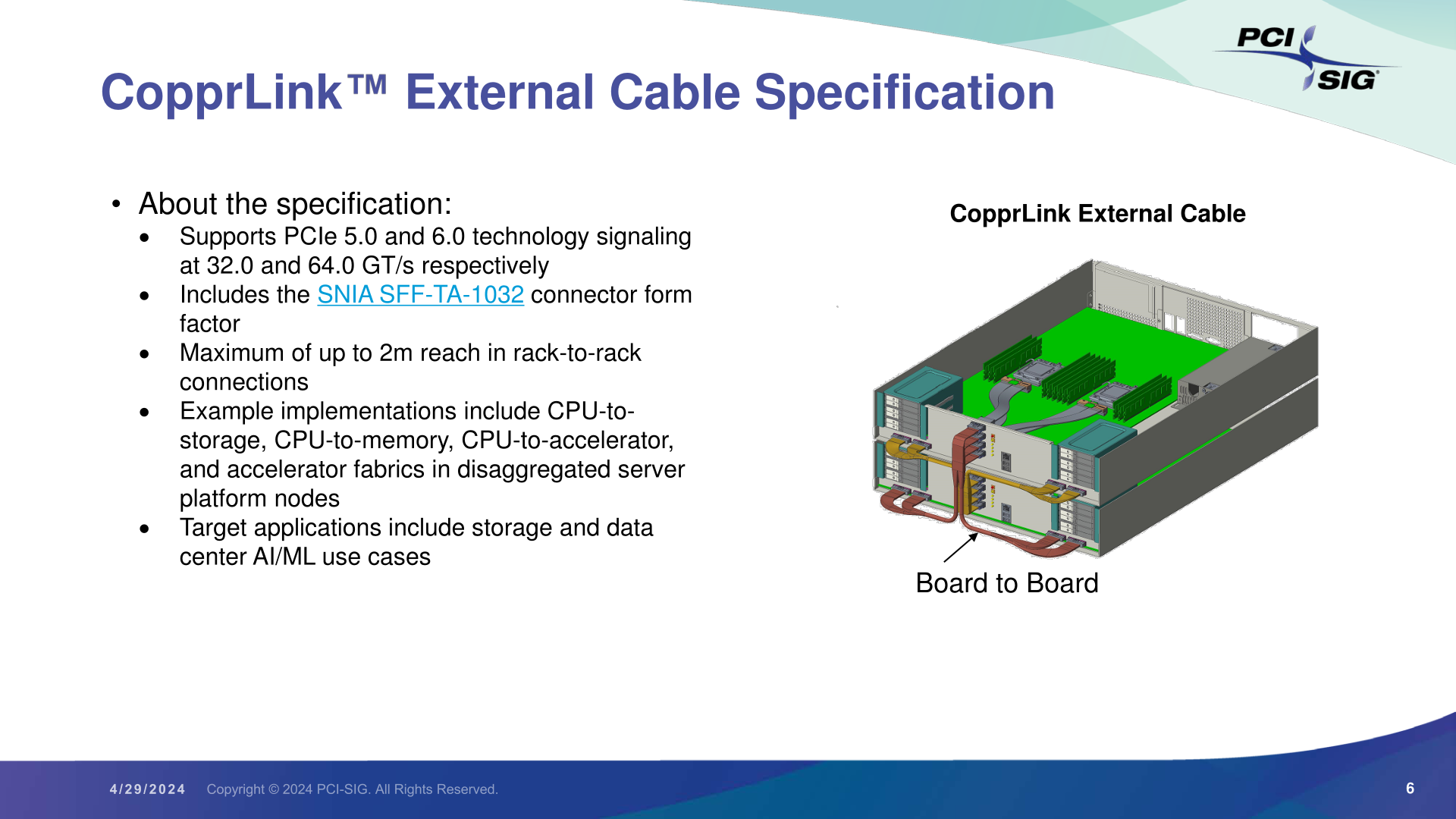

Meanwhile, the group has also developed an external cabling standard to cover those same PCIe 5.0/6.0 data rates. External CopprLink cables can go up to 2 meters, allowing for board-to-board connections within a rack, and even short rack-to-rack PCIe connections.

The external version of CopprLink also uses a more robust connector, relying on SNIA’s SFF-TA-1032 standard. Like internal/1016, this is available with x4, x8, and x16 configurations, using 44, 68, and 120 positions/pins respectively. The PCI-SIG is expecting this version of the standard to be primarily adopted by the AI/Machine Learning markets, which need to move heaps of data between systems. Notably, however, they don’t really expect the storage market to make use of this spec – instead, they’ll be served by an updated version of the classic PCI Express External Cabling standard.

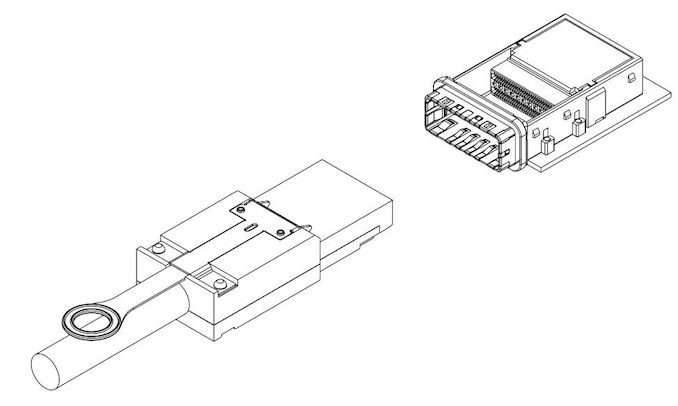

SFF-TA-1032 x16 Plug and Connector (Figure 4-1, Image Courtesy SNIA)

Finally, a bit farther out on the group’s roadmap, PIG-SIG is also reiterating that they’re working on a new optical cabling standard as well. The workgroup for this project was established in 2023, so the project is still in its early days. Notably, the forthcoming optical standard is intended to be optical technology-agnostic, allowing for PCIe to be paired with a variety of optical technologies.

In the meantime, with the internal and external CopprLink standards completed, the PCI-SIG is hoping to quickly move this cabling into production. Since these are solely cabling standards – and thus don’t require intensive development efforts such as new controllers or the like – the group is hoping that their members will have something to show off in time for the group’s developer conference this summer, or the Flash Memory Summit in August. After which, hardware vendors should be able to deploy the new cables relatively quickly.

Source: PCI-SIG

8 Comments

View All Comments

Dr_Mobeyos - Wednesday, May 1, 2024 - link

They should have gone for an opto-eletic parallel interface, cause thats where we are heading in a few years with NPU cards anyway. ReplyFallen Kell - Tuesday, May 7, 2024 - link

The only issue with that would be dealing with bend radius issues related to an optical cable. Easier to go copper than to deal with the inevitable issues of fragile optical cables. Replyballsystemlord - Wednesday, May 1, 2024 - link

I'm surprised they don't have a PCIe 4.0 standard in the above page 15 slide. Did they omit it from the slide or did the standard never exist? ReplyLiKenun - Saturday, May 4, 2024 - link

If I recall, OCuLink’s PCIe 4.0-capable update was in the works. 4.0 cables exist, but I don’t think the standard was ever released officially.(I have OCuLink cables, adapters, and enclosures professing PCIe 4.0 capability, but have often found stability lacking.) Reply

JTWrenn - Thursday, May 2, 2024 - link

Hopefully this will lead to new formfactors for larger m.2 speed ssd's. ReplyFallen Kell - Tuesday, May 7, 2024 - link

That is what the U.2 format (and U.3) are for. ReplyHresna - Sunday, May 5, 2024 - link

I wonder if this might enable some more novel form factors for SFF pc motherboards with fewer compromises, or perhaps curtail the need of bulky and unwieldy gpu riser cables for some designs ReplyDougMcC - Sunday, May 5, 2024 - link

With more than 4x the bandwidth of displayport/hdmi and a reach of 2m I wonder if anyone is thinking about using this to deliver data to displays. Reply